The Industry’s First EDA tool based on

Open-Source Software

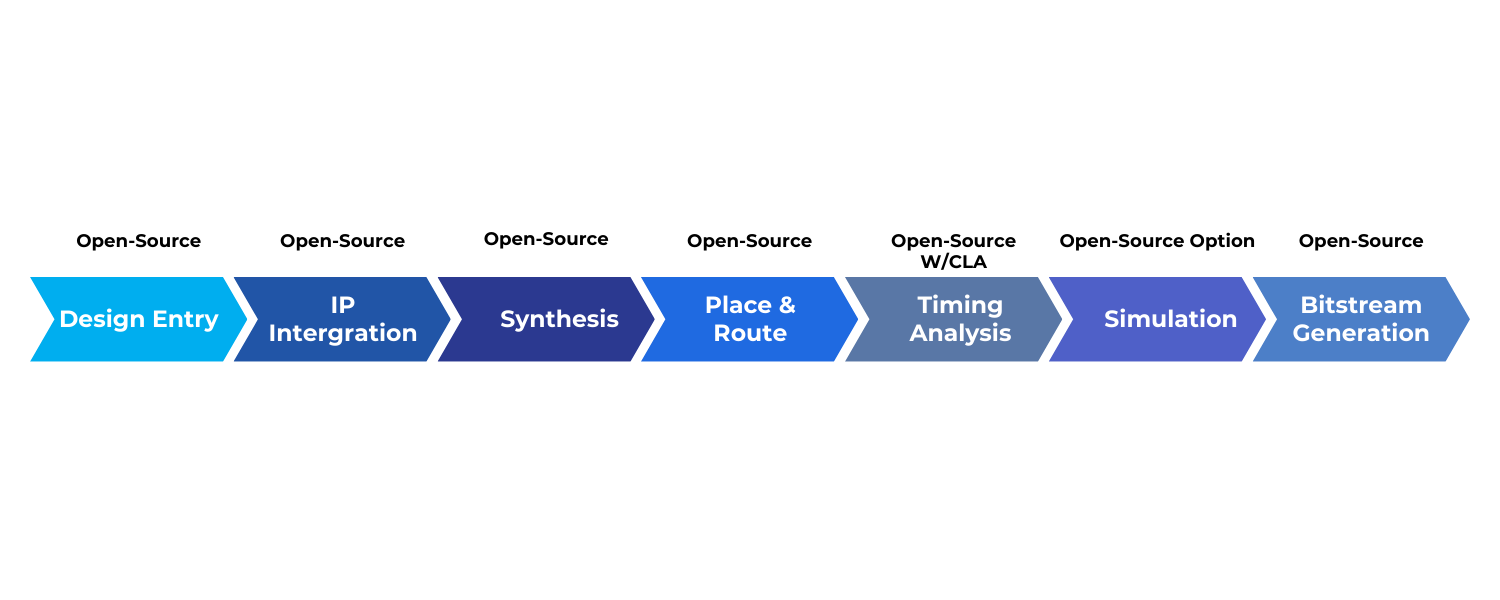

As NeuLink’s primary design environment Raptor features a rich GUI, while being built on the backend by industry standard TCL. As the world’s first commercial FPGA EDA environment based on end-to-end open-source tooling, Raptor’s entire FPGA design flow is supported by Open-Source, from project creation all the way through to bitstream generation

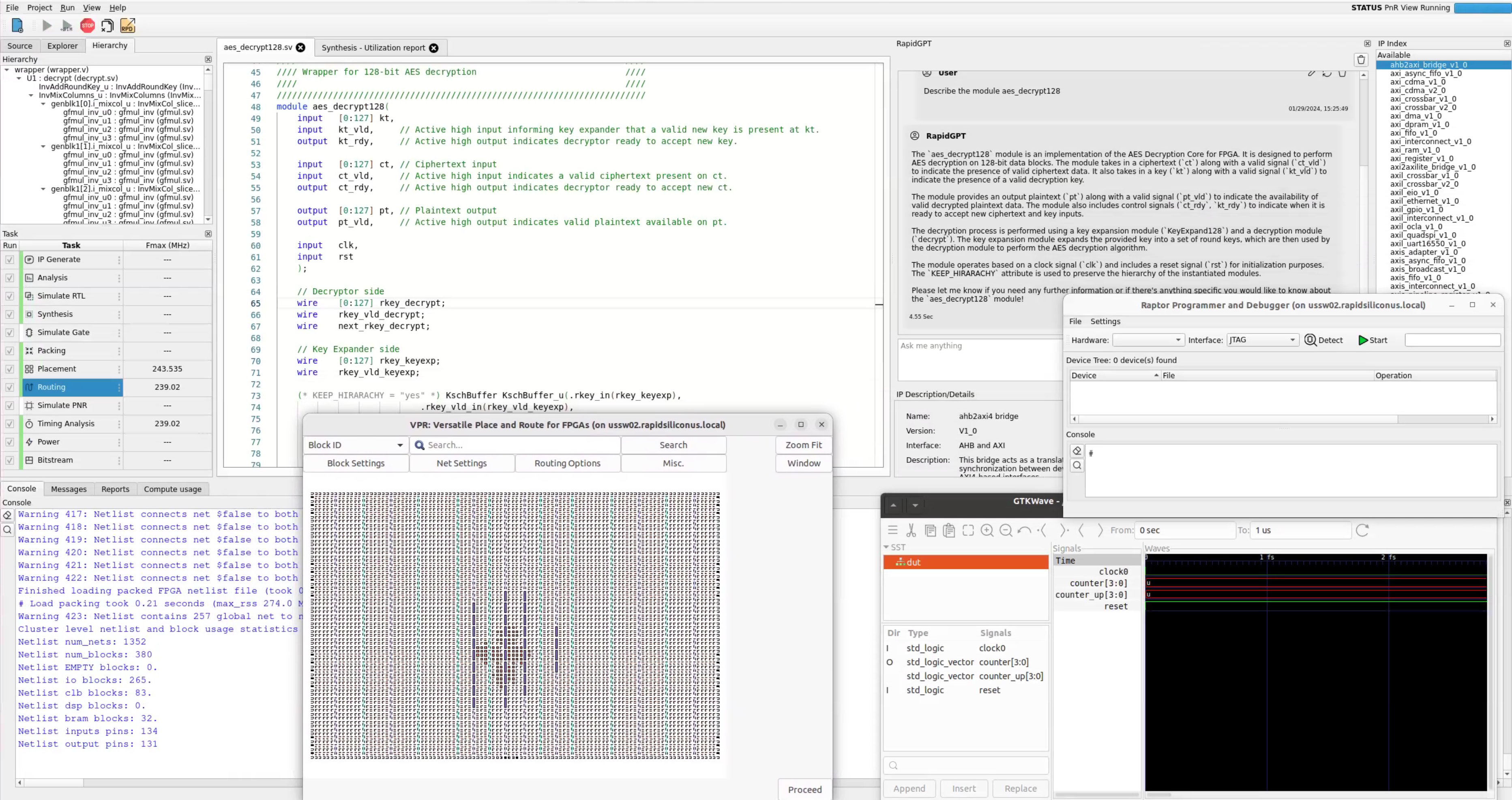

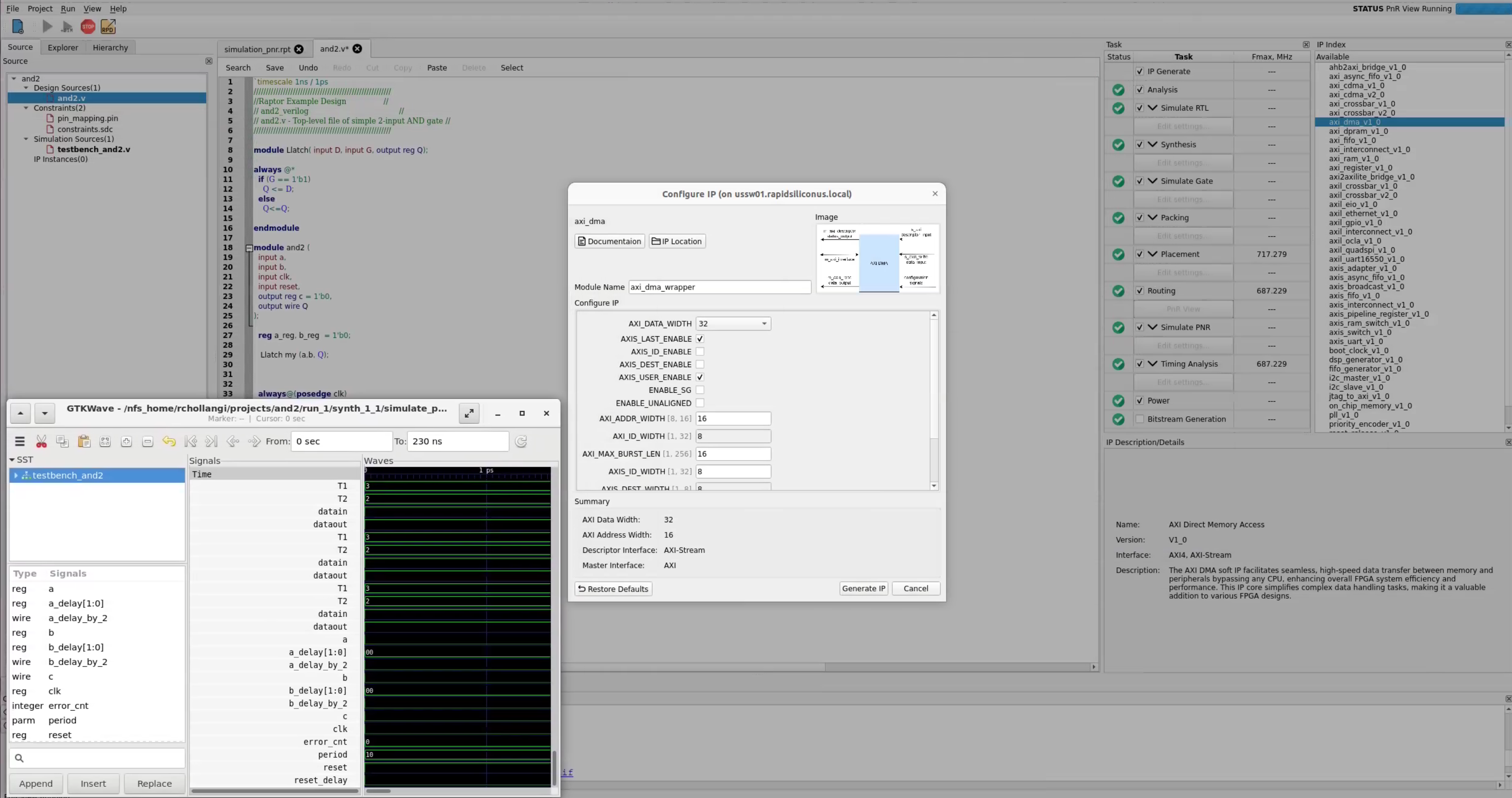

Design Entry and IP Integration

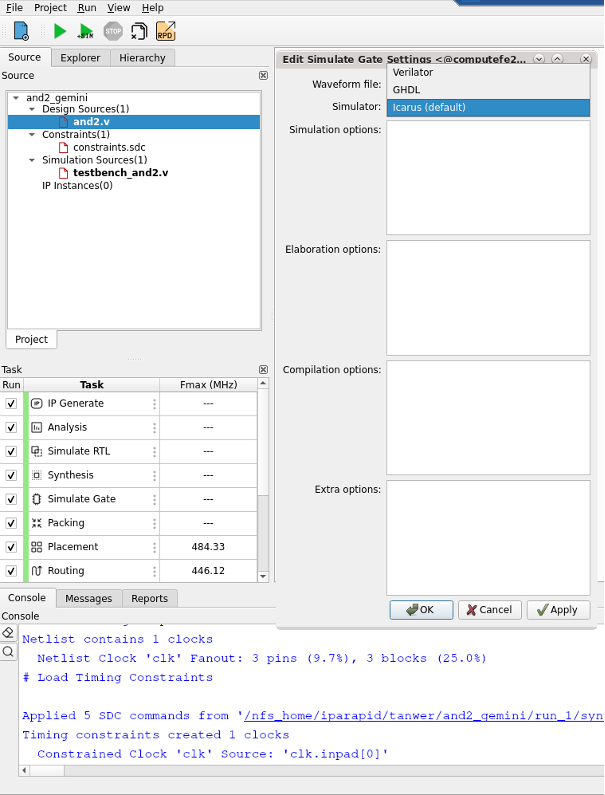

Raptor simplifies the design entry process by welcoming designers into a FOEDAG-based GUI environment supporting Verilog, System Verilog, and VHDL design files. The intuitive interface, backed by an industry-standard TCL backend, ensures a smooth entry into FPGA design. Additionally, Raptor enhances traditional IP integration with Litex, enabling Python-to-RTL capability for automated IP generation. Designers can leverage Python code and explore Raptor’s extensive IP catalogue, featuring over 50 Soft-IPs, to expedite project development with pre-built IP blocks

Synthesis, Place & Route, Timing Analysis, and Simulation

Raptor’s synthesis engine combines the strength of Yosys with the innovative ABC-DE (AI-Based Design Exploration), resulting in a 3x reduction in area through dynamic synthesis and smart pruning. The Place & Route process is executed using the robust VPR (Versatile P&R) engine, known for its efficiency and reliability, contributing not only to the Raptor Design Suite but also to the OpenFPGA framework. For precise timing analysis, Raptor employs OpenSTA, an industry-standard engine. Integrated simulation engines Icarus and GHDL, with Verilator support for System Verilog, ensure comprehensive simulation capabilities, backed by the GTKwave Waveform Viewer for thorough visualization in both RTL and Gate Level Simulations

Bitstream Generation and RPE – NeuLink’s Power Estimator & Board Tool