NeuFPGA

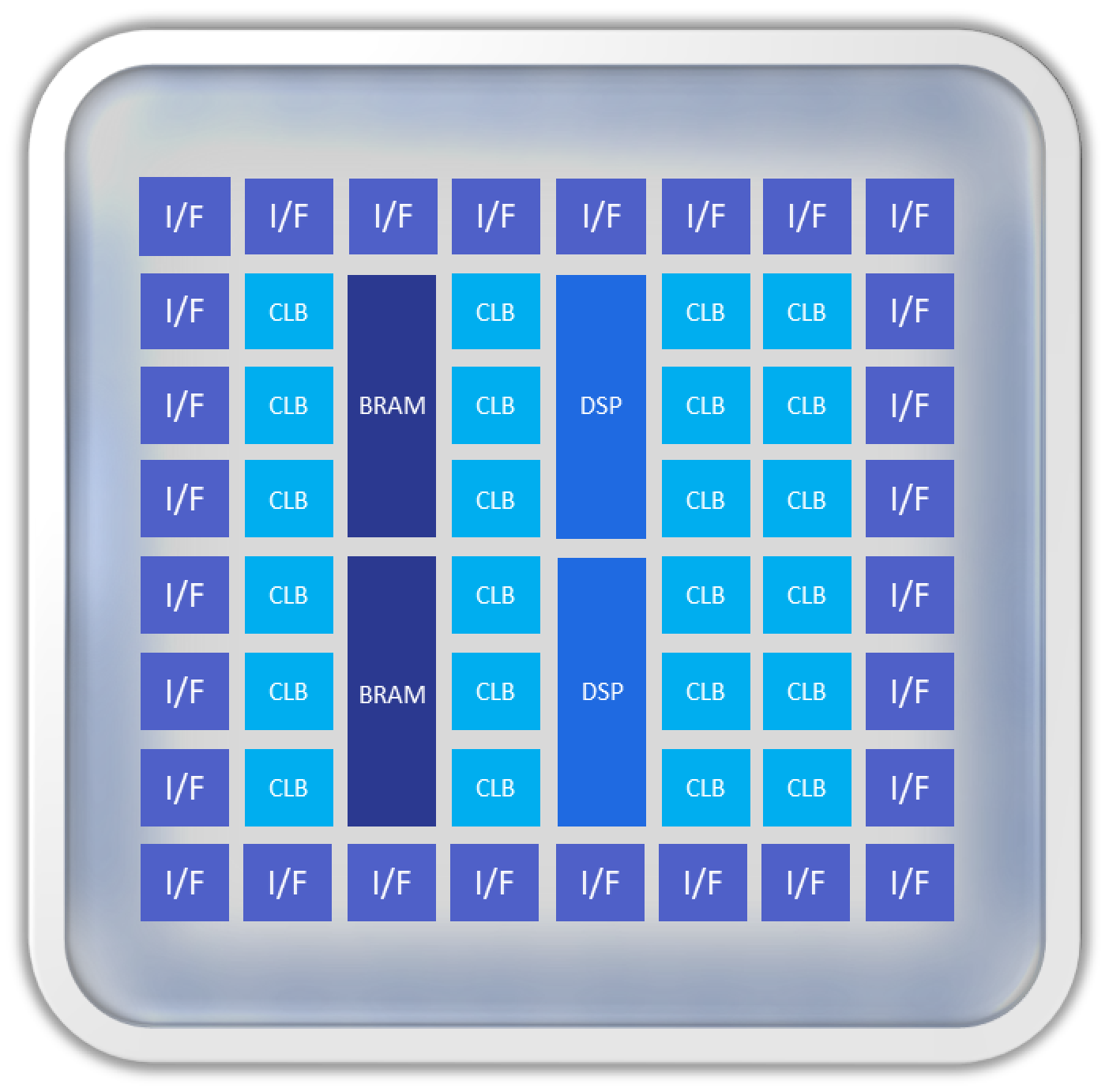

NeuFPGA Fabric IP is generated based on an Open Source framework developed by the University Of Utah under the project name – OpenFPGA. NeuLink has made several improvements to improve the PPA of the FPGA IP generated by this framework to make it more suitable for commercial use in Intelligent Edge Applications

Features

Customizable & Scalable Architecture:

- Customize your FPGA as you need using our versatile modular architecture

- Specify your own Logic, DSP and RAM requirements for your FPGA

- Design your FPGA that perfectly matches your vision and application demands

Advanced Digital Signal Processing:

- Process arithmetic operations at 15% lowered dynamic power against competing architectures

- Fracturable 18×20-bit multipliers with 64-bit accumulators for complex arithmetic operation

- Fixed coefficient support for efficient filtering applications including FIR

Optimized Memory Access:

- Fracturable and configurable 36-Kb RAM blocks for improved efficiency and flexibility

- Supports parity and multiple data widths and depths

- Dedicated FIFO mode with flags

Improved Logic Capabilities:

- Experience fracturable 6-input look-up-tables (LUTs) integrated with fast adders

- Efficient and seamless implementation of complex logic functions

- Ensure optimal performance and resource utilization for your FPGA application

Multi-Purpose IO Subsystem:

- Flexible IO capability supporting High-Range and High Performance IOs

- Supports over 35 single-ended and differential IO standards ranging from 1.2 to 3.3V

- Selectable slew rates, drive strengths, termination and pull up/down resistors