What is NeuPro?

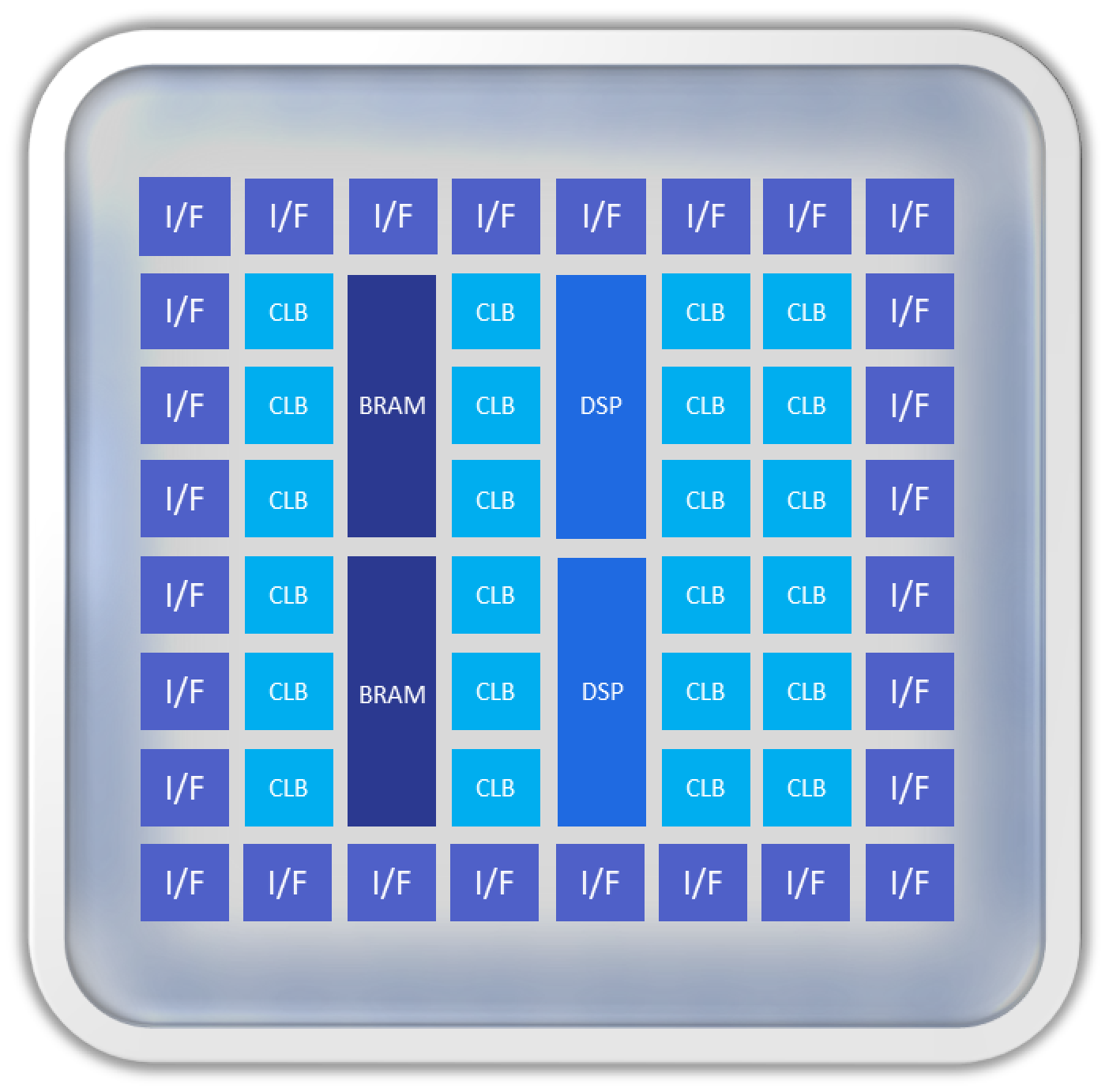

NeuPro Embedded IP is an area and power-efficient customizable SRAM-based FPGA IP that can be implemented in your next ASIC to allow future customization, improvements and future-proofing of your next design

You specify the mix of logic, RAMs and DSP to meet the application needs and when coupled with the powerful Raptor Design Suite allows design refinement, updates and enhancements post-tapeout and even post deployment reducing the time and risk for the overall chip design and extending the overall life-cycle of the product

Configurable Logic Block

The configurable logic block (CLB) is the primary logic resource. The CLB features eight, 6-input programmable Look-Up Tables (LUTs) with optional configurability to 64-bit LUTRAM and/or shift-register LUTs. Each LUT is fraturable to a dual-5-input LUT and can drive an independent register featuring clock enable and reset for a total of 16 registers in the CLB

A fast carry chain is also incorporated for efficient implementation of arithmetic operations. The tile-able architecture ensures seamless scalability for tailored requirements and efficient topologies

Block-RAM

True Dual Port 1024 x 36-bit single RAM: Enables simultaneous Read/Write and separate clocks providing faster access to large amount of data

Fracturable 1024 x 18-bit RAM blocks: Optimizes memory access for improved efficiency

Supports various data widths: x1, 2, 4, 9, 18, 32, 38-bit with parity for all configurations of 9-bit or wider

Registered inputs with optional output registration: Streamline pipelining for faster memory access times

FIFO mode with flags: Allows for specific data processing order with flags including for threshold for full, empty, almost full/empty, underrun, and overrun

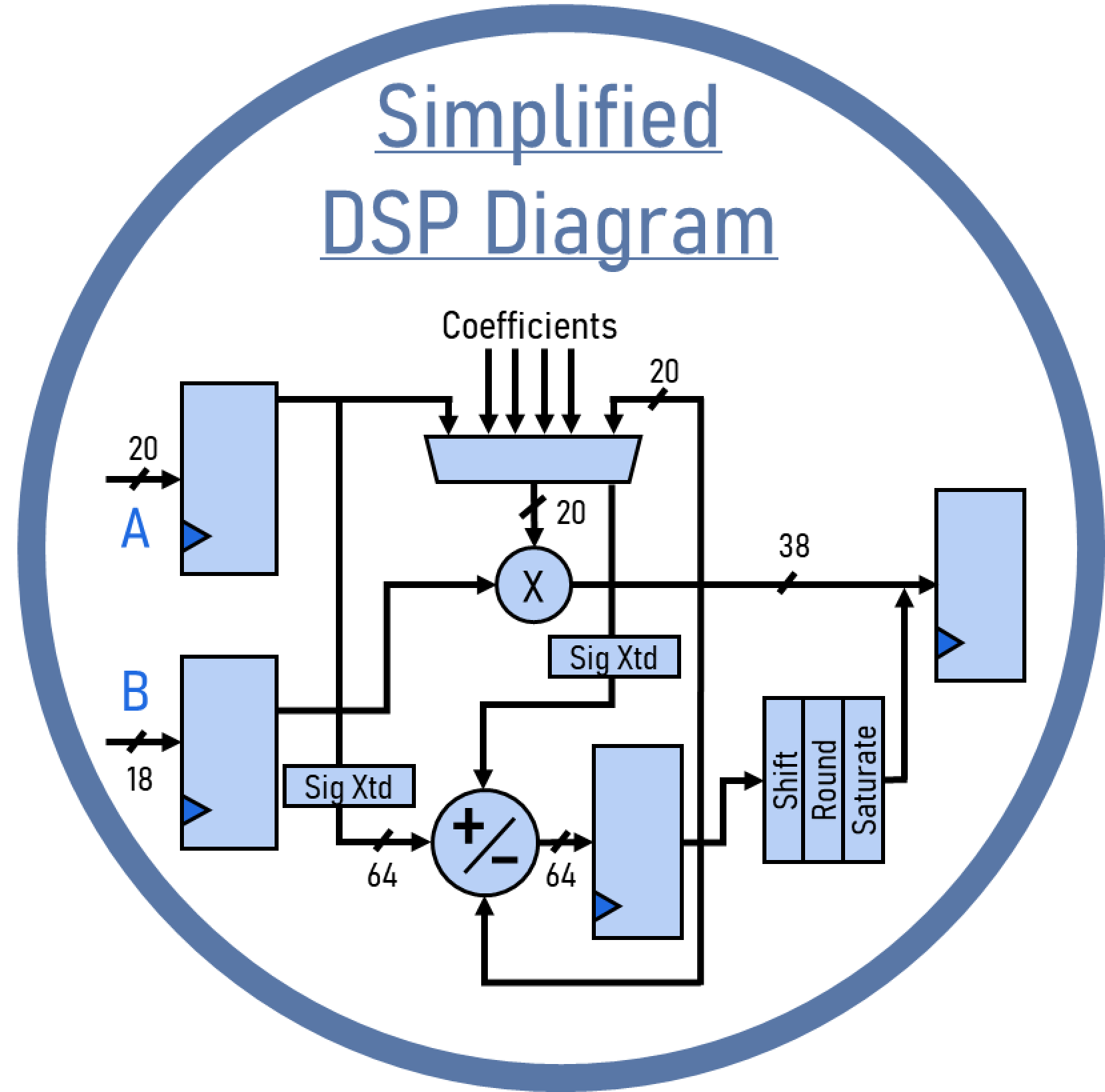

DSP Block

The DSP block, featuring 18×20-bit multipliers with 64-bit accumulators is fractuarble to two, 9×10-bit multipliers with 32-bit accumulators for efficient implementation of smaller operands. This versatile solution supports fixed coefficients, dynamic signed/unsigned operands, rounding, saturation and internal data shifting while delivering heightened performance through programmable internal pipeline stages. The DSP block ensures seamless and efficient arithmetic processing capabilities, making it an ideal choice for a variety of applications

Clocking and I/O

NeuPro Embedded IP has a balanced clock routing topology that allows up to 16 clocks to source any CLB, BRAM or DSP in the array at speeds up to 500 MHz. Up to 4 programmable PLLs can source the clock allowing clock smoothing and flexible frequency synthesis for the clocking requirements as well as generating high-speed clocks up to 3 GHz for fast external I/O data capture.

Two types of flexible I/O are available. A high-range single-ended or differential I/O capable of supporting 17 I/O standards from 1.8 to 3.3 volts. Additionally, a high-performance single-ended or differential I/O supporting 22 I/O standards from 1.2 to 1.8V with speeds up to 1.5 GHz.

Performance and Efficiency

Transition into the future of FPGA technology with NeuPro, setting new benchmarks by surpassing current commercial-grade FPGA devices. NeuPro offers a remarkable 40% improvement in resource utilization compared to FPGAs with LUT-4 logic elements, a 20% increase in Fmax over commercially available FPGAs of the same class, and system-level performance exceeding 300 MHz at the same time consuming up to half the power dissipation

Discover why your business needs NeuPro Embedded IP, providing unparalleled flexibility and performance for your ASICs and SoCs, whether customizing to specific needs, seamlessly integrating and verifying into your SoC design, or enjoying custom process node portability. NeuPro ensures your business stays at the forefront of programmable logic innovation