Virgo FPGA

Virgo builds on the Vega FPGA IP to deliver a stand-alone FPGA solution that can add programmability and augmentation to any board design. Whether coupled with an ASIC or used alone to encapsulate the design functionality, Virgo is a cost–effective and power efficient way to build advanced design functionality

Fabric and Performance

Virgo is comprised of CLB , BRAM, and DSP blocks to form the base functionality. This is connected via a robust clocking network allowing up to 16 clocks and 4 PLLs, allowing clocking performance up to 500 MHz and multiple logic-level design performance exceeding 300 MHz.

The Raptor Design Suite implements the front-to-back FPGA design featuring efficient synthesis while producing high-performance results

DDR Memory and High-Speed Transceivers

The larger Virgo devices also include a 32-bit wide DDR3/LPDDR3/DDR4/LPDDR4 PHY and controller supporting data-rates up to 2133. The memory is connected to the fabric via a 64-bit AXI slave bus allowing full data bandwidth transmission to the application

Four 16 Gbps configurable high-speed transceivers are also included supporting a variety of common protocols. These can be coupled with a hardened PCIe Gen4x4 controller to allow anywhere from Gen1x1 to Gen4x4 support for your application connectivity

Configuration

A RISC-V-based configuration engine securely and efficiently loads the configuration bitstream data to the device to realize its end functionality. Being RISC-V allows additional customization to the loading and configuration of the FPGA that many other devices cannot offer. The configuration sub-system has a SPI/QSPI interface for configuration data storage and has several other interfaces (JTAG, UART, I2C) available for debug and configuration engine communications. The configuration circuitry has an optional PUF with 256-bit AES encryption for secure bitstream storage

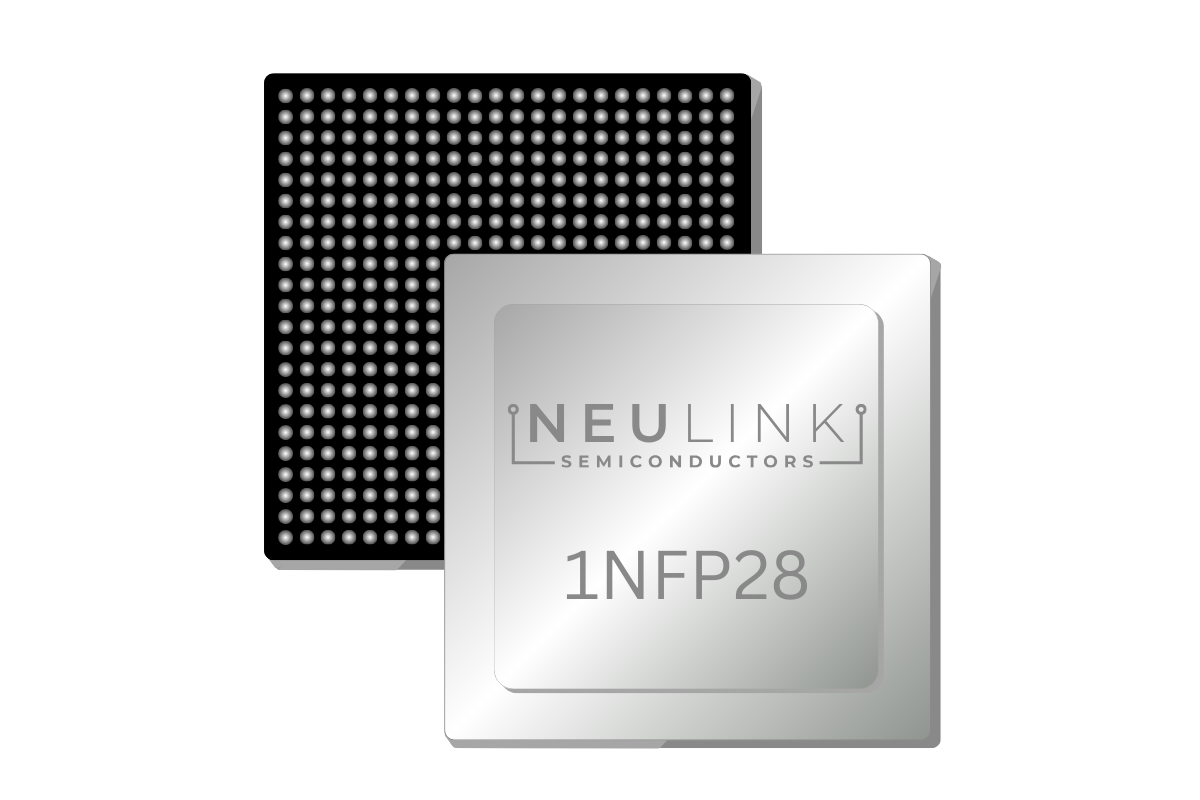

Packaging

NeuLink uses lidded and lidless flip-chip packaging utilizing on-package capacitors and optimized ball layouts resulting in a high-performance, small footprint device that requires fewer additional passive and active components on the board. Additionally, both the lidless and lidded packages offer superior thermal dissipation realizing lesser cooling needs. The optimized BOM generally results in a very cost-optimized and board area efficient design

If you are interested in FPGA IP added to your next ASIC, consider the Vega Embedded FPGA

If you need a processing system with your FPGA, consider the Gemini SOC FPGA